## 7. BUSINESS OVERVIEW

## 7.1 HISTORY

The history of our business can be traced back to the establishment of SkyeChip in 2019, where we subsequently commenced IC design operations by developing silicon IPs in Penang in 2020.

The table below sets out the key events and milestones in the history and development of our business:

| Calendar Year | Key Event and Milestone                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2020          | We commenced our IC design operations by developing silicon IPs. We secured our first contract for the design of memory interface IPs, namely DDR3 in 2020.                                                                                                                                                                                                                                             |

|               | We also secured our first contract for a custom silicon IP covering various interface protocols including DDR3 and DDR4 within a single IP.                                                                                                                                                                                                                                                             |

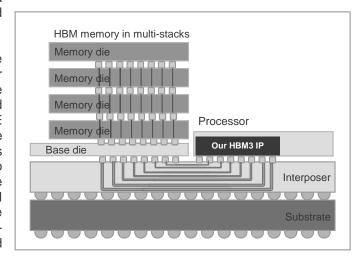

|               | In the same year, we also initiated the design and development of memory interface IPs, namely HBM3.                                                                                                                                                                                                                                                                                                    |

|               | We initiated our first patent application for the invention of silicon IPs based on our design and development works. As at the LPD, we have developed a series of inventions, where 108 were filed for patent applications in Malaysia as well as in foreign countries including China and the USA. Out of these, 29 patents have been registered and 79 patents are pending application/registration. |

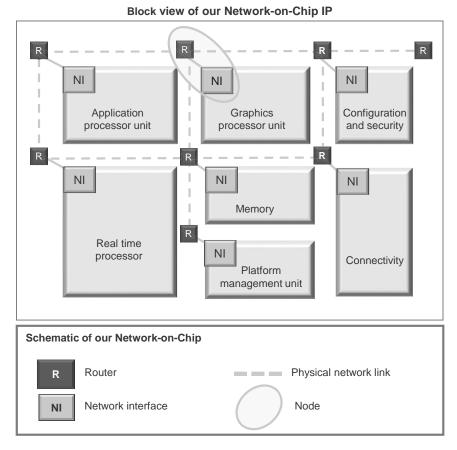

| 2021-2022     | In 2021, we initiated design and development works for the Network-on-Chip IPs.                                                                                                                                                                                                                                                                                                                         |

|               | In 2022, we secured our first contract for coherent Network-on-Chip IP design and development, where we licensed our Network-on-Chip IP to a fabless semiconductor company.                                                                                                                                                                                                                             |

|               | In 2022, we secured a contract for the design of a custom silicon IP covering various interface protocols including DDR, LPDDR, LVDS and MIPI.                                                                                                                                                                                                                                                          |

| 2023-2024     | In 2023, we secured a contract for the licensing of HBM3 memory interface IP, which includes a fully integrated controller, PHY and I/O.                                                                                                                                                                                                                                                                |

|               | In the same year, we also secured a contract to develop a custom silicon IP, namely low-power low-latency memory interface IP.                                                                                                                                                                                                                                                                          |

|               | We also expanded into the design and development of custom ASIC. In 2023, we secured two contracts with a customer to jointly develop two IoT ASICs with the incorporation of our silicon IPs.                                                                                                                                                                                                          |

|               | In 2024, we expanded our silicon IP portfolio where we launched new and enhanced silicon IPs including HBM3E and a new generation of Network-on-Chip IP.                                                                                                                                                                                                                                                |

|               | In 2024, we secured a contract with a customer to develop custom ASIC for AI inference with the incorporation of our silicon IPs. In the same year, we commercialised our first IoT ASIC, which has completed the system and software development, pilot run and mass production.                                                                                                                       |

|               | In 2024, we were granted the Malaysia Digital Status from MDEC for our IC design solutions. With the Malaysia Digital Status, we are entitled to certain incentives, rights and privileges from the Government of Malaysia, subject to necessary approvals, compliance of applicable conditions, laws and regulations.                                                                                  |

| 2025          | In January 2025, we joined the Intel Foundry Accelerator IP Alliance, which provides us with access to Intel Foundry's advanced process technologies, complementing our silicon IP design and development capabilities.                                                                                                                                                                                 |

| Calendar Year | Key Event and Milestone                                                                                                                                                                                                               |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | In July 2025, we expanded our silicon IP portfolio where we commercialised new silicon IPs, including D2D interface IP, as well as enhanced silicon IPs including LPDDR5 and LPDDR5x.                                                 |

|               | In September 2025, we secured a contract for the development of RISC-V SoC, with the incorporation of RISC-V processor cores integrated with various silicon IPs, including our Network-on-Chip IP and other third-party silicon IPs. |

## 7.2 AWARDS AND RECOGNITIONS

Since the commencement of our business in 2020 and up to the LPD, we have 29 patents registered in Malaysia, China and the USA, and 79 patents pending application/registration in Malaysia, China and the USA. See Annexure A of this Prospectus for further details on our patents.

Since the commencement of our business and up to the LPD, we have received the following awards and recognitions:

| Year | Awarding party                                                   | Award / Recognition                                                                                                                                               |

|------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2023 | Ministry of Investment, Trade and Industry, Malaysia             | Certificate of acknowledgement as a Mission-based Project Champion – Create global IC design champions in EV, RE and AI under the New Industrial Master Plan 2030 |

| 2023 | The Institution of Engineering and Technology (Malaysia Network) | Platinum Award for Industry Excellence Award 2023                                                                                                                 |

#### 7.3 OVERVIEW OF OUR BUSINESS

#### 7.3.1 Our business model

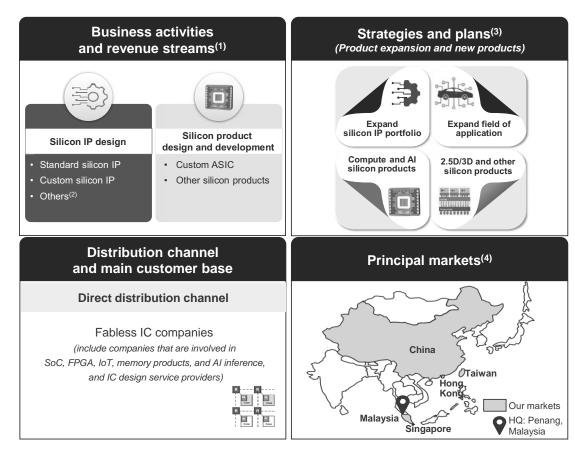

Our business model is as follows:

## Notes:

- (1) For the FYEs 31 March 2023 and 31 March 2024, our revenue was mainly contributed by the design of standard and custom silicon IPs. The design and development of custom ASIC commenced in September 2023. For the FYE 31 March 2025, the revenue contribution from the silicon IP design segment accounted for 73.3% of our total revenue, mainly from standard and custom silicon IPs, while the custom ASIC segment accounted for the remaining 26.7% of our total revenue.

- (2) Include design services based on requests from customers for the FYEs 31 March 2024 and 31 March 2025, as well as design of memory test systems for the FYE 31 March 2025.

- (3) See Section 7.5 of this Prospectus for details on our strategies and future plans.

- (4) Revenue contribution from China accounted for 61.5%, 72.8%, and 56.5% of our total revenue for the FYEs 31 March 2023, 31 March 2024 and 31 March 2025 respectively. This is followed by Taiwan which accounted for 31.5%, 24.8%, and 33.5% of our total revenue for the FYEs 31 March 2023, 31 March 2024 and 31 March 2025 respectively. See Section 7.3.3 of this Prospectus for details of our revenue segmentation by geographical markets.

#### 7.3.2 Business activities and revenue streams

We are principally involved in IC design specialising in silicon IPs and silicon products including custom ASIC. We provide licensable silicon IPs to our customers to integrate into their IC products. We also design and develop custom ASIC products tailored to meet specific customer requirements, delivering semiconductor chips that are optimised for a specific application rather than for general-purpose use.

As an original IC design company, we own the IP rights to our designs. As at the LPD, we have developed a series of inventions, of which 29 patents have been registered in Malaysia, China and the USA, and 79 patents are pending application/registration in Malaysia, China and the USA.

We have access to PDKs from foundries that enable us to design ICs on advanced process nodes down to 4nm. We also have access to interposer PDK and package design rules from OSAT partners, which allow us to carry out interposer and package design for 2.5D/3D packaging.

We use a range of IC design software tools and methodologies, including EDA tools to design, simulate, analyse and verify our IC designs. We also maintain and run our own server farms and computing infrastructure to support our IC design activities. As at the LPD, our IC Design and Software Design team consists of 318 technical personnel, including architects, logic design engineers, analogue circuit design engineers, physical design engineers, package design engineers and software engineers. Our team is led by our Chief Technology Officer, Teh Chee Hak.

Silicon IP refers to pre-designed and pre-verified building blocks or modules that can be integrated into larger IC designs. These building blocks are reusable and customisable, which help to accelerate development and reduce design risks of licensees by providing tested and reliable building blocks. Our designs adhere to international standard-setting bodies such as JEDEC and UCle.

We are involved in IC design for standard and custom silicon IPs, where standard silicon IPs include memory interface IP, Network-on-Chip IP and D2D interface IP.

## (i) Standard silicon IP

Our standard silicon IPs accounted for 44.6%, 62.4% and 62.6% of our total revenue for the FYEs 31 March 2023, 31 March 2024 and 31 March 2025 respectively. As our standard silicon IPs are to be integrated into our customers' IC products, our standard silicon IPs are designed in accordance with industry standards to ensure compatibility across various memory suppliers. These IP blocks are commonly used to accelerate the design process of larger ICs. Our standard silicon IP portfolio is as follows:

- **Memory interface IP:** Our memory interface IP manages data communications between the computing core and memory. When the computing core requires data, our memory interface IP retrieves it from the memory device and transfers it for processing. After processing, the memory interface IP sends the data back to the memory device for storage. Our memory interface IP includes a memory controller IP, a PHY IP and an I/O IP. This is a memory interface IP, which refers to self-contained blocks designed for efficient memory management.

- **Network-on-Chip IP:** We design Network-on-Chip interconnect IP that focus on both physical and logical infrastructure to ensure efficient data routing within a SoC. Network-on-Chip serves as the communication pathway connecting multiple components within a SoC. Our Network-on-Chip IPs are configurable to meet specific application needs and performance requirements. We provide IC design for both coherent and non-coherent Network-on-Chip IPs.

D2D interface IP: Our D2D interface IP is designed to facilitate high-speed communication between different functional blocks within a multi-die package, such as a CPU, GPU and FPGA, or other processors configured in 2D, 2.5D or 3D structures. Our D2D interface IP includes both a controller and PHY block.

To support the integration and configuration of our standard silicon IPs, we offer in-house proprietary memory system firmware solutions.

## (ii) Custom silicon IP

Our custom silicon IPs accounted for 55.4%, 36.6% and 9.2% of our total revenue for the FYEs 31 March 2023, 31 March 2024 and 31 March 2025 respectively. Our custom silicon IPs are designed based on individual customer specifications and requirements, which will be integrated into our customers' IC products. This includes multi-interface protocol IPs that support different standards and communication protocols such as DDR, LPDDR, MIPI, LVDS and multi-standard I/O interfaces.

In addition, we have designed and developed a custom low-power, low-latency memory interface IP tailored for specific applications. This IP is optimised to minimise power consumption and enhance memory protocol handling, thereby improving data flow between computing cores and memory. To support the integration and configuration of our custom silicon IPs, we offer in-house proprietary memory system firmware solutions.

## (iii) Silicon products

#### **Custom ASIC**

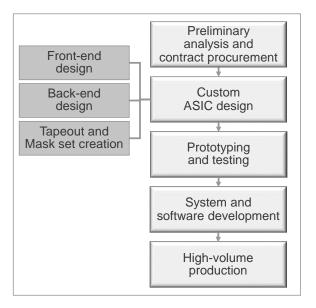

We expanded into the design and development of custom ASIC in September 2023. A custom ASIC is a semiconductor chip designed for a specific application rather than for general-purpose use. For the FYE 31 March 2025, revenue contribution from the custom ASIC segment accounted for 26.7% of our total revenue.

Custom ASIC is designed to perform targeted functions with enhanced efficiency in power consumption and performance, a reduced physical footprint and the ability to execute proprietary algorithms that standard devices are unable to support efficiently. Additionally, custom ASIC provides improved IP protection as functionality is embedded at the hardware level, safeguarding proprietary technology and processes from reverse engineering.

#### Other silicon products

In September 2025, we expanded into the development of other silicon products, where we secured a contract for the development of RISC-V SoC. This development involves the incorporation of RISC-V processor cores integrated with various silicon IPs, including our Network-on-Chip IP and other third-party silicon IPs.

## (iv) Others

Revenue from the others segment accounted for 1.0% and 1.5% of our total revenue for the FYEs 31 March 2024 and 31 March 2025 respectively. This includes design services based on requests from customers as part of our integrated customer support services, as well as design of memory test systems.

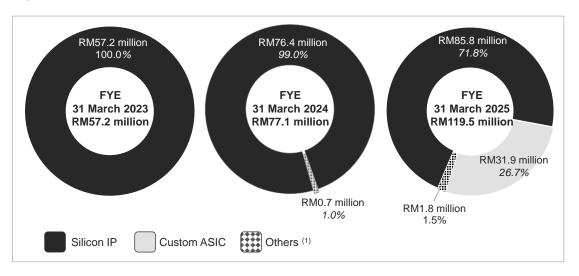

For the Financial Years Under Review, our revenue segmentation by products and services is depicted below:

#### Note:

(1) Include design services based on requests from customers for the FYEs 31 March 2024 and 31 March 2025, as well as design of memory test systems for the FYE 31 March 2025.

Further breakdown of our revenue segmentation by products and services is set out in the table below:

|                         | FYE 31 March   |       |        |       |         |       |  |

|-------------------------|----------------|-------|--------|-------|---------|-------|--|

|                         | 2023           |       | 2024   | 1     | 202     | :5    |  |

| Revenue                 | RM'000         | %     | RM'000 | %     | RM'000  | %     |  |

| Silicon IP segment      | 57,159         | 100.0 | 76,327 | 99.0  | 85,739  | 71.8  |  |

| Standard silicon IP (1) | <i>25,4</i> 86 | 44.6  | 48,115 | 62.4  | 74,771  | 62.6  |  |

| Custom silicon IP       | 31,673         | 55.4  | 28,212 | 36.6  | 10,968  | 9.2   |  |

| Custom ASIC segment     | -              | -     | -      | -     | 31,934  | 26.7  |  |

| Others                  | -              | -     | 736    | 1.0   | 1,830   | 1.5   |  |

| Total revenue           | 57,159         | 100.0 | 77,063 | 100.0 | 119,503 | 100.0 |  |

## Note:

(1) Includes memory interface IP and Network-on-Chip IP, of which the breakdown for the Financial Years Under Review is as follows:

|                     | FYE 31 March |      |        |      |        |      |  |

|---------------------|--------------|------|--------|------|--------|------|--|

|                     | 2023         |      | 2024   |      | 2025   |      |  |

| Revenue             | RM'000       | %    | RM'000 | %    | RM'000 | %    |  |

| Memory interface IP | 7,482        | 13.1 | 28,099 | 36.4 | 47,169 | 39.5 |  |

| Network-on-Chip IP  | 18,004       | 31.5 | 20,016 | 26.0 | 27,602 | 23.1 |  |

| Total               | 25,486       | 44.6 | 48,115 | 62.4 | 74,771 | 62.6 |  |

## 7.3.3 Principal markets

We principally operate in Penang, Malaysia and mainly serve foreign customers. Within foreign markets, China and Taiwan collectively accounted for 93.0%, 97.6%, and 90.0% of our total revenue for the FYEs 31 March 2023, 31 March 2024 and 31 March 2025 respectively. This is followed by Singapore at 2.4% and 1.0% of our total revenue for the FYEs 31 March 2024 and 31 March 2025 respectively, and Hong Kong at 0.9% of our total revenue for the FYE 31 March 2025. Meanwhile, Malaysia accounted for 7.0% and 8.1% of our total revenue for the FYEs 31 March 2023 and 31 March 2025 respectively.

The breakdown of our revenue by geographical markets for the Financial Years Under Review is as follows:

|                 |        |       | FYE 31 N | March |         |       |

|-----------------|--------|-------|----------|-------|---------|-------|

|                 | 2023   |       | 2024     | 2024  |         | 5     |

|                 | RM'000 | %     | RM'000   | %     | RM'000  | %     |

| Foreign markets | 53,175 | 93.0  | 77,063   | 100.0 | 109,799 | 91.9  |

| China           | 35,171 | 61.5  | 56,124   | 72.8  | 67,473  | 56.5  |

| Taiwan          | 18,004 | 31.5  | 19,136   | 24.8  | 39,997  | 33.5  |

| Singapore       | -      | -     | 1,803    | 2.4   | 1,237   | 1.0   |

| Hong Kong       | -      | -     | -        | -     | 1,092   | 0.9   |

| Malaysia        | 3,984  | 7.0   | -        | -     | 9,704   | 8.1   |

| Total revenue   | 57,159 | 100.0 | 77,063   | 100.0 | 119,503 | 100.0 |

#### 7.3.4 Distribution channels and customers

We utilise a direct distribution channel strategy, securing contracts directly with customers who use our products and services. Our customers are fabless IC companies including companies that are involved in SoC, FPGA, IoT, memory products and AI inference, as well as IC design service providers. Our direct distribution channel strategy enables us to work closely with customers to address their specific needs and specifications. Additionally, we provide customised solutions and services, including design support for integration and implementation. This approach fosters strong customer relationships and also positions us to secure more projects from each customer.

For the Financial Years Under Review, all our revenue was derived from direct distribution channels where our revenue by customer type is as follows:

|                             |        |       | FYE 31 M |       |         |       |

|-----------------------------|--------|-------|----------|-------|---------|-------|

|                             | 2023   |       | 2024     |       | 2025    |       |

|                             | RM'000 | %     | RM'000   | %     | RM'000  | %     |

| Direct distribution channel | 57,159 | 100.0 | 77,063   | 100.0 | 119,503 | 100.0 |

| Fabless IC companies        | 57,159 | 100.0 | 77,063   | 100.0 | 119,503 | 100.0 |

| Total revenue               | 57,159 | 100.0 | 77,063   | 100.0 | 119,503 | 100.0 |

#### 7.4 OUR COMPETITIVE STRENGTHS

Our competitive strengths which will provide us with the platform to sustain and grow our business, are as follows:

## 7.4.1 We have designed and commercialised multiple high-performance and high-bandwidth memory interface IP to drive our business growth and sustain our competitive advantages

As at the LPD, we have designed and commercialised multiple high-performance, high-bandwidth memory interface IPs, including LPDDR4, LPDDR4x, LPDDR5, LPDDR5x, as well as HBM3 and HBM3E. These memory interface IPs deliver efficient data transfer and meet the rigorous demands of advanced applications, which drive our business growth and strengthen our competitive position in the semiconductor industry.

In addition, we continue to develop the next generations of memory interface IPs, including LPDDR6 and HBM4. These advancements will facilitate the continuing relevance of our services to meet ever-increasing improvements in performance as well as to sustain and grow our business.

## 7.4.2 We have access to advanced technologies down to a 4nm process node supported by foundries as well as certain third-party design tool providers

As an IC design company, it is essential for us to stay at the forefront of technological changes, innovations and advancements, particularly in the fast-evolving field of ICs and electronics. The short product life cycles of electronic devices often drive the demand for greater processing power while reducing device size, requiring more components, such as transistors, to fit into smaller semiconductor areas.

We have access to PDKs from foundries to design ICs using advanced process nodes down to 4nm. These PDKs supply essential design rules, simulation models and documentation that ensure our designs meet manufacturability and yield requirements. In addition, we also have access to EDA tools and Verification IPs from third-party design tool providers. EDA tools and Verification IPs are specialised and essential tools for IC design. See Section 7.13 of this Prospectus for further details on the technologies used.

In addition to our IC design operation, access to advanced technologies is crucial for our new ventures into custom ASIC design and development, especially for applications requiring high performance, power efficiency and a smaller form factor. This capability is demonstrated by our successful tapeout of two IoT ASICs, which had incorporated our silicon IPs. As at the LPD, the prototypes of our IoT ASICs were completed in April 2024 and September 2024 respectively. One of these IoT ASICs has been commercialised in September 2024 and the second IoT ASIC is planned for commercialisation by end-2025.

Access to advanced technologies gives us a significant advantage by enabling us to meet the technological requirements of a diverse customer base, thus supporting our business growth. Additionally, these advanced technologies enhance our internal R&D efforts, allowing us to develop innovative IC designs that can address emerging business opportunities and sustain our growth.

# 7.4.3 We are the original designer of our standard silicon IP featuring reconfigurability which enables us to license our products to multiple customers, providing us with a modular and scalable business model to sustain and drive our business growth

We have designed and commercialised standard silicon IPs, including memory interface IP, Network-on-Chip IP and D2D interface IP, which were developed in-house entirely. As such, we retain full IP rights to these designs. Our library of standard silicon IPs allows for scalable business growth, as each silicon IP can be licensed as is or reconfigured to meet each customer's operating environment across various countries. This silicon IP enables us to license them to multiple customers or projects, providing a robust portfolio that supports and drives our business growth. This approach offers a significant business advantage, as it eliminates the need to invest substantial time and resources in developing each silicon IP for each new customer.

Our standard silicon IP is configurable, allowing us to customise it to meet each customer's specific needs while still conforming to industry standards. This flexibility ensures that our IP can be reused across a range of applications and customers with minimal modifications. We launched our standard silicon IP in 2022 (FYE 31 March 2023) and our revenue from standard silicon IP increased by 88.8% to RM48.1 million for the FYE 31 March 2024 (FYE 31 March 2023: RM25.5 million), followed by further growth of 55.4% to RM74.8 million for the FYE 31 March 2025.

Our current business model involves right-to-use sales of our silicon IP, while retaining the intellectual property rights to these designs. Customers are granted the right to use our IP exclusively for the specific projects outlined in their licensing contracts. This approach not only ensures ongoing ownership of our IP but also provides an opportunity for additional revenue if our IP is used in other products or projects.

## 7.4.4 We have successfully commercialised both coherent and non-coherent Network-on-Chip IPs which will help grow our business

Network-on-Chip IP is essential for managing on-die communication infrastructures in complex multi-core ICs, ensuring high-efficiency, high-performance and low-power data transactions. Our Network-on-Chip technology provides us with the platform to address increasingly complex IC designs as chips move towards more advanced process nodes carrying out more extensive processing requiring efficient and quality transmission and reception of data in SoC. This will provide relevance to our design in meeting changing and innovative technologies to grow our business.

Our Network-on-Chip technology offers several advantages over traditional interconnect methods such as bus-based, point-to-point, hierarchical, ring, and cross-bar switches. These advantages include improved scalability, performance, modularity, flexibility, fault tolerance and power efficiency. As a result, Network-on-Chip is a popular choice for modern SoC designs, especially in systems with high complexity and performance demands. See Section 7.7.6 of this Prospectus for more details on the benefits of Network-on-Chip.

In addition, we offer both coherent and non-coherent Network-on-Chip IPs, enabling us to support a wide range of IC products. We have the capability to integrate both coherent and non-coherent Network-on-Chip architectures within the same chip. This dual capability allows us to address a broader market, including high-performance computing, AI and consumer electronics. See Section 7.7.6 of this Prospectus for more details on the coherent and non-coherent Network-on-Chip IPs.

Our expertise in designing both coherent and non-coherent Network-on-Chip IPs is crucial for our business growth. This capability requires advanced skills and provides us with a significant competitive edge to meet the evolving market demands. Our capabilities are further enhanced by the commercialisation of our latest Network-on-Chip IPs in 2024. These latest Network-on-Chip IPs includes non-coherent Network-on-Chip IP with expanded protocol support and improvements in power, performance and area, as well as coherent Network-on-Chip IP with enhanced topology support to reduce latency.

Our coherent and non-coherent Network-on-Chip IPs are engineered for high bandwidth, low power consumption and reduced latency in multi-processor semiconductors. They offer flexible configuration and reliable performance, making them highly attractive to potential customers and driving our business growth. Additionally, we plan to leverage our non-coherent Network-on-Chip architecture to explore new applications in the automotive sector in the future.

## 7.4.5 We have in-house developed proprietary software that provides ease of use to configure our Network-on-Chip IP into our customers' ICs

We have our in-house developed proprietary software to support the configuration of our Network-on-Chip IP into our customers' ICs. Our proprietary software is typically packaged with our Network-on-Chip IP for use by our customers, which are tools designed to optimise system performance for configuration and integration. See Section 7.7.6 of this Prospectus for more information on our in-house developed proprietary software.

Our in-house developed proprietary software, bundled with our Network-on-Chip IP, offers convenience to our customers by simulating and optimising interconnect performance, as well as ensuring seamless integration of our Network-on-Chip IP into their overall ICs. This software, RAPTuner, is designed to add value to our Network-on-Chip IP, enhancing its appeal and encouraging the purchase of our Network-on-Chip IP.

## 7.4.6 We have experienced Executive Directors backed by a skilled technical team to sustain and further develop our business

Our business is led by our Chief Executive Officer, Dato' Fong Swee Kiang and Chief Technology Officer, Teh Chee Hak.

Dato' Fong Swee Kiang has over 35 years of experience in the semiconductor industry. He has held positions at the Intel group of companies where he was responsible for overseeing the development of central processing units, chipsets and IPs, while leading a team of engineers. Additionally, he has worked at Altera Corporation (M) Sdn Bhd ("Altera Malaysia"), an Intel Corporation related company following its acquisition of Altera Corporation in 2015, leading the company's R&D operations in Malaysia, driving innovation and development initiatives. He has also served as Director of Operations and Senior Operations Director at Avago Technologies (Malaysia) Sdn Bhd ("Avago Technologies"), a Broadcom Inc. related company, managing the company's global operations and overseeing new product introductions before founding SkyeChip which commenced business in 2020. He is responsible for leading our Group's business strategy, overseeing operations, sales and marketing and ensuring financial health while managing our Group's business and investment stakeholders.

Teh Chee Hak has over 20 years of experience in the semiconductor industry. He began his career at Intel Microelectronics (M) Sdn Bhd ("Intel Microelectronics"), where he was responsible for the architecture and microarchitecture of central processing units, memory, I/O and platform controller hubs and IPs, as well as completing assignments in the USA. He then joined Altera Malaysia as a principal engineer before progressing to the role of architect where he was responsible for designing and implementing the memory interface architecture and microarchitecture of FPGA products and IPs. He transitioned back to Intel Microelectronics as a principal engineer and subsequently served as chief architect at Intel Microelectronics where he focused primarily on the overall architecture and microarchitecture of FPGA products and IPs. He joined SkyeChip in 2020 where he is responsible for overseeing our Group's technical strategy and leading the design and development of advanced IPs and ASICs for Al and high-performance computing applications.

As at the LPD, our technical team comprises 318 professionals who hold degrees, diplomas or certificates in relevant disciplines. Our team is led by our Chief Technology Officer, Teh Chee Hak. These technical experts are essential in our design and development operations, as well as providing engineering support to our customers.

See Section 9 of this Prospectus for further details on our Executive Directors and technical personnel.

## 7.4.7 Our business has experienced high revenue growth demonstrating the acceptance of our products and services to serve as the platform for further business growth

Since the commencement of our business in 2020, we have shown consistent revenue growth. From the FYEs 31 March 2023 to 31 March 2025, our revenue increased at a CAGR of 44.6%, reaching RM119.5 million for the FYE 31 March 2025. This robust revenue growth reflects the strong market acceptance of our products and services and provides a solid platform for further expansion. Building on the success of our current suite of silicon IPs, we are actively developing several new products to drive continued growth. See Section 7.5 of this Prospectus for further details of our strategies and future plans.

We continue to capitalise on our competency in silicon IP design by investing in innovation and integrating our silicon IPs with new product developments. This approach not only enhances our silicon IP offerings but also allows us to expand into ASIC design and development. By demonstrating our adaptability and technical expertise, we are able to drive growth and explore new opportunities in the industry. This is demonstrated by our contracts secured with customers for the design and development of two IoT ASICs and an AI inference ASIC. These contracts bundle our silicon IP with our ASIC design capabilities, demonstrating our ability to integrate both hardware and IP effectively. See Sections 7.7.8 to 7.7.10 of this Prospectus for further details.

Our expertise in silicon IP design includes supporting and ensuring interoperability for multiple interface protocols and specific interface requirements, while optimising power, performance and area for various applications. Additionally, our ability to design and validate IP in accordance with industry standards such as JEDEC and UCIe enhances our reputation for technical competence. This serves as a platform to secure new contracts, driving business growth and expanding our revenue base in the future.

## 7.4.8 We have the ability to provide custom silicon IP for our customers to foster customer loyalty and secure new contracts

One of our key strengths is our technical expertise in designing custom silicon IP tailored to meet the specific requirements of each customer. This includes optimising performance, power efficiency and functionality needs, as well as the ability to modify and enhance designs based on customer feedback and evolving requirements. We provide comprehensive support including design, integration and prototype bring-up assistance to facilitate the productisation of our customers' IC products. This capability fosters customer loyalty and helps us secure new business opportunities.

Our strengths are supported by our team of technical personnel with expertise and knowledge in various aspects of silicon IP design and IC development. Our technical personnel including engineers increased from 38 personnel in 2020 to 318 personnel as at the LPD.

Furthermore, our custom silicon IP offerings allow us to provide optimised solutions to customers of a wide range of electronic products ranging from consumer products, such as wearable devices, to industrial and communication applications, as well as IoT and AI applications. This will provide us with a potentially large addressable market to grow our business as well as to mitigate against risks of a downturn in one or a small number of user groups or sectors.

Revenue contribution from our custom silicon IP accounted for RM31.7 million (55.4%), RM28.2 million (36.6%) and RM11.0 million (9.2%) of our total revenue for the FYEs 31 March 2023, 31 March 2024 and 31 March 2025 respectively. Our ability to successfully deliver our custom silicon IP serves as a platform to grow our business and customer base.

## 7.4.9 We are engaged in various industry standard definition bodies including JEDEC, UCle and PCI-SIG that enable us to participate in early discussions on the evolving IP standards

Industry standard bodies such as JEDEC, UCle and PCI-SIG are essential for IP as they ensure interoperability and compatibility, which is crucial for integrating various IPs and modules into a functional system. Therefore, incorporating these standards into our IP design is vital to ensure interoperability and compatibility for market acceptance to support the sustainability and growth of our business.

As a member of JEDEC, UCle and PCI-SIG, we are involved in defining and reviewing the emerging standards. Our involvement with these global standard-setting bodies provides us with advanced insights into emerging trends, potential revisions and new standards. This enables us to proactively adapt our designs to evolving requirements, ensuring that we remain competitive and relevant, and continue to grow our business.

#### 7.5 OUR STRATEGIES AND FUTURE PLANS

In 2024, Malaysia's electrical and electronic (E&E) exports recorded RM601.6 billion, with electronic ICs accounting for 52.0% of the total E&E exports. Malaysia's semiconductor strength primarily lies in its back-end services, such as assembly, packing and testing. A key strategic development of the New Industrial Master Plan 2030 (NIMP 2030) is to elevate Malaysia's position within the E&E value chain by shifting towards front-end activities such as IC design, advanced packaging and expanding wafer fabrication capabilities. (Source: IMR Report)

Our strategies and future plans are aligned with the NIMP 2030 to enhance high-value-added activities within the semiconductor and electronics industry value chain. NIMP 2030 was launched in 2023 to strengthen IC design capabilities, enabling Malaysia to capitalise on rapidly growing sectors such as electric vehicles, renewable energy and AI (Source: IMR Report).

Going forward, we will leverage our expertise in silicon IP and IC design to capitalise on both existing and new opportunities in the IC design and semiconductor industry. We will also stay relevant with technological innovations to drive our business expansion and growth.

## Overview of our strategies and future plans

## 7.5.1 Expansion of silicon IP portfolio and field of application

## (a) Expand silicon IP portfolio

Our strategies and future plans are to capitalise on our competency in standard and custom silicon IP by continuing to invest in silicon IP innovations. We plan to expand our silicon IP portfolio to drive business growth and increase our revenue base. This expansion includes designing and developing a new generation of Network-on-Chip IP and memory interface IP.

We have successfully designed and delivered multiple custom silicon IPs that incorporate multiple memory interface standards within a single IP. As at the LPD, we have successfully designed and commercialised multiple memory interface IPs, including LPDDR4, LPDDR4x, LPDDR5, LPDDR5x, as well as HBM3 and HBM3E. These represent some of the current versions of the memory interface IPs with high data throughput that supports advanced computing requirements. Our capabilities are further demonstrated by the commercialisation of our latest Network-on-Chip IP in 2024, which includes coherent and non-coherent Network-on-Chip IPs. This new generation Network-on-Chip IP feature expanded protocol support, improved power efficiency, enhanced performance, and reduced latency and area, making them ideal for a wide range of applications, from edge computing to data centres.

We carry out continuous R&D to keep abreast of evolving technologies to improve the performance of our memory interface IPs. As part of our strategies and future plans, we aim to develop new memory interface IPs, including LPDDR6 and HBM4, in the future, featuring improved efficiency and performance, and increasing data transfer rates. This will help us meet growing demand for end-market applications such as mobile and consumer electronics, networking, edge computing and high-performance computing.

The table below depicts our strategies and future plans to develop new generations of memory interface IPs with the target specifications as below:

|                                |        | Do      | uble Data R | High Bandwidth Memory |           |      |       |                     |

|--------------------------------|--------|---------|-------------|-----------------------|-----------|------|-------|---------------------|

| Target specification           | LPDDR4 | LPDDR4x | LPDDR5      | LPDDR5x               | LPDDR6(1) | нвм3 | нвмзе | HBM4 <sup>(1)</sup> |

| Maximum data rate (Gb/s)       | 3.2    | 4.267   | 6.4         | ≥8.5                  | 14.4      | 6.4  | ≥8.0  | ≥8.0                |

| Total data width per component | 64     | 64      | 64          | 64                    | 96        | 1024 | 1024  | 2048                |

| Maximum total bandwidth (GB/s) | 25.6   | 34.1    | 51.2        | ≥68.3                 | 172.8     | 819  | ≥1024 | ≥2048               |

| Energy efficiency (pJ/bit)     | ~7-10  | ~7-10   | ~5-7        | ~2-3                  | ~2-3      | ~0.6 | ~0.6  | ~0.4-0.5            |

#### Note:

Note: Values in the table are approximate and can vary based on specific implementation, operating condition and workload characteristics

We are leveraging our expertise in software and firmware development to venture into the EDA tool licensing model in the future to establish a new revenue stream. In addition to Network-on-Chip IP design and development, we provide technical assistance with the use of our in-house developed proprietary software to support the integration and configuration of our Network-on-Chip IP into our customers' ICs. Our proprietary software is typically packaged with our Network-on-Chip IP for use by our customers. Our in-house designed and developed integration and configuration software includes RAPTuner (a network architecture simulation and optimisation tool).

Our existing knowledge in silicon IP design is complemented by proprietary EDA tools that are designed specifically for optimisation, verification and validation. This will offer customers a complete silicon IP design suite that integrates IP configuration, testing and performance analysis. The development of EDA tools that are pre-integrated with our own silicon IP will streamline the process for our customers who use our silicon IP in their design.

## (b) Expand new field of application – automotive silicon IP

Our current silicon IP portfolio is designed to meet the needs of high-performance computing, mobile communications, IoT, Al and data centre applications. As part of our strategic expansion, we plan to expand into the automotive IP market to capitalise on the growing opportunities, driven by the increasing demand for advanced automotive technologies.

The new automotive IP will be able to support critical technologies such as in-vehicle networks and vision systems, which are essential for ADAS and autonomous driving. These technologies enable accurate and comprehensive information transmission within vehicles, ensuring safety, power efficiency and performance.

A key focus of the automotive IP development will be on our Network-on-Chip IP. To meet the requirements of the automotive industry, the new silicon IP is required to adhere to functional safety standards, including compliance with ISO 26262. As at the LPD, our team is in the process of refining the IP to meet the requirements and we plan to commercialise the new automotive silicon IP between 2026 and 2027.

The estimated cost for our silicon IP portfolio expansion and new field of application expansion is approximately RM[●] million for a period of 36 months from the date of our Listing between 2026 and 2029, which will be funded through the gross proceeds from our Public Issue. See Section 4.5 of this Prospectus for further details on the use of proceeds.

<sup>(1)</sup> The target specification for intended products

## 7.5.2 Design and develop compute and Al silicon products

We plan to design and develop new compute and AI silicon products to address the rising demand for high-performance, energy-efficient processing in data centres and AI applications. This is done by incorporating our pre-designed and pre-verified interface and interconnect silicon IP which will lead to faster development times compared to developing everything from scratch.

The new compute and AI silicon products will focus on two segments as described below:

## (i) Custom compute and Al hardware accelerator

Custom compute and AI hardware accelerators are ASICs designed for AI and large-scale data workloads. They offload specialised tasks, such as tensor math and input data preprocessing, from general-purpose CPUs/GPUs into dedicated hardware engines. This approach offers the flexibility needed to handle large-scale data operations while improving overall system efficiency and reducing overall power consumption. Key examples include:

- Data preprocessing hardware accelerator: A dedicated hardware that

processes raw data before it reaches the AI or compute engine. It handles data

formatting, cleaning, resizing, compression, and error checking, which reduces

data transfer and power consumption while enabling the main processors to

focus on computational workloads.

- Security ASIC products: Custom-designed products optimised for cryptographic operations, secure processing and hardware-based security functions. These ASICs are widely used in trusted computing, secure communications, authentication and anti-tampering applications.

The development process involves integrating our interface and interconnect IPs with third-party IPs, and customers' proprietary IPs. To expand our custom ASIC offerings, we plan to enter into joint-development arrangements with technology partners. These partnerships will allow us to tap into their system architecture and software expertise, complementing our silicon IP design and development capabilities. As at the LPD, we have not entered into any arrangements for the joint development of new compute and AI hardware accelerators.

## (ii) High-performance CPU and AI platforms

We also plan to expand our silicon products to develop high-performance CPU and AI platforms that combine CPU-grade general computing capabilities and AI acceleration for the server and edge computing environment.

In March 2025, Malaysia announced a 10-year partnership worth USD250 million (approximately RM1.1 billion) with ARM Holdings Plc ("ARM") to acquire various IP licences, including 7 ARM Compute Subsystem ("CSS") and 25 ARM Flexible Access ("AFA") tokens, and to train 10,000 engineers. This is part of the national initiative, Silicon Vision, which offers opportunities for semiconductor and IC design companies to participate and grow within the local ecosystem. As at the LPD, we have submitted our application for access to one CSS platform and one AFA platform, and is currently pending the decision of relevant regulatory authorities.

In line with our strategy to expand our silicon product offerings, we plan to design and develop new high-performance CPU and AI platforms. High-performance CPU and AI platforms are designed to optimise performance for a server and edge computing environment.

By leveraging our technical expertise and strength in memory interface and Networkon-Chip IPs, the development of the new high-performance CPU and AI platforms involves several areas:

- architecture definition and microarchitecture design focusing on optimising specific performance, power and area targets;

- integration of other silicon IP to complete the chip design, such as memory interfaces, high-speed I/O interfaces, custom accelerators for AI/ML, networking, cache hierarchies and security features;

- verification and simulation to ensure it functions correctly and meets performance targets, and is free of errors;

- physical design including translation from high-level design into a physical layout in geometric data file (GDSII) format involving placement and routing of components;

- tape-out for fabrication; and

- final processes after fabrication including testing and validation alongside system and software development.

The development and implementation of the new high-performance CPU and AI platforms are predicated upon securing access to the ARM CSS and related IP technologies, which are subject to specific qualification criteria.

To expand our product offerings, we plan to enter into joint-development arrangements with technology partners. These partnerships will allow us to tap into their system architecture and software expertise, complementing our silicon IP design and development capabilities. As at the LPD, we have not entered into any arrangements with potential technology partners for the joint development of new high-performance CPU and AI platforms.

The estimated cost for our compute and AI silicon products expansion is approximately RM[•] million for a period of 36 months from the date of our Listing between 2026 and 2029, which will be funded through the gross proceeds from our Public Issue. See Section 4.5 of this Prospectus for further details on the use of proceeds.

#### 7.5.3 Design and develop 2.5D/3D and other silicon products

As part of our strategies and future plans, we target to extend our IC design capabilities to design and develop new 2.5D/3D and other silicon products, addressing opportunities in advanced semiconductor packaging. This includes the following key areas:

## (i) CIM silicon dies

We plan to design and develop CIM silicon dies, leveraging our expertise in memory interface IP design and development.

Traditionally, data is stored in memory and transferred to processing units for computation, with the processed data then sent back to memory for storage. This constant data movement often creates bottlenecks, increases latencies and raises power consumption, particularly in data-intensive applications.

To address these challenges, we plan to develop CIM silicon dies that integrate computational capabilities directly within or near the memory chip, utilising the 2.5D/3D chip packaging technologies. This approach eliminates the need for data transfer between memory and processing units, significantly improving performance, efficiency and power consumption. As such, CIM silicon dies are particularly beneficial for applications that require rapid and efficient processing of large datasets, such as AI and machine learning acceleration, as well as high-performance computing workloads.

## (ii) I/O chiplets

As part of our new product development plans, we will design and develop 2.5D/3D I/O silicon products to facilitate I/O communications in systems where multiple dies or chips are placed side-by-side on an interposer (2.5D) or vertically stacked (3D).

#### This includes:

- Memory I/O chiplets, which are designed to facilitate rapid data access between memory stacks and processors. These chiplets can be integrated into larger advanced packages with the high-performance processors, such as those used in high-performance computing and AI, to enable high-bandwidth, low-latency access to memory.

- D2D interconnect chiplets, to provide high-speed connectivity between chiplets using advanced D2D communication standards, such as UCIe, to reduce latency and enable scalable multi-chip architectures.

- Chiplet-based accelerator, which is a custom processing unit designed to perform matrix multiplication, tensor computation, inferencing and cryptographic functions, improving compute core efficiencies and system security.

The I/O chiplets are designed to scale with increasing demand, such as the increase in number of dies in 2.5D/3D advanced packaging. These I/O chiplet silicon products are designed to meet specific power, performance, area and cost requirements.

The estimated cost for the design and development of these new 2.5D/3D and other silicon products is approximately RM[●] million for a period of 36 months from the date of our Listing between 2026 and 2029, which will be funded through the gross proceeds from our Public Issue. See Section 4.5 of this Prospectus for further details on the use of proceeds.

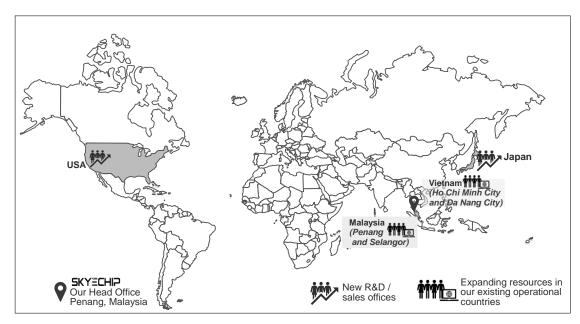

## 7.5.4 Establish and expand facilities and resources

We are scaling up our facilities including setting up new R&D and sales offices to cater to our continuing business and product expansion as well as increasing our technical resources to enhance our capabilities for the design and development of new silicon IPs and products.

A snapshot of our facility and resource expansion plans is set out below:

## (i) Establishment and expansion of R&D and sales offices

We intend to establish and/or expand our R&D and/or sales offices in the following markets progressively between 2026 and 2029:

|          | 2026       | 2028-2029    |            |

|----------|------------|--------------|------------|

|          | R&D office | Sales office | R&D office |

| Malaysia | ✓          |              |            |

| Vietnam  | ✓          |              |            |

| Japan    |            | ✓            |            |

| USA      |            | ✓            | ✓          |

In December 2024, we commenced our initial operations in Ho Chi Minh City and Da Nang City, Vietnam utilising co-working spaces, and plan to relocate to dedicated offices as we expand our operations between 2026 and 2029. As at the LPD, we have hired 19 technical personnel for our Vietnam operations.

For our domestic operations, we plan to expand our R&D office space in Malaysia between 2026 and 2029 to support our business expansion and product development plans. In addition, we intend to expand our foreign presence by establishing and/or expanding R&D and/or sales offices in Vietnam, Japan and the USA. By securing office space in these markets, we aim to expand our access to local talents, which will enable us to broaden our technical capabilities and market reach, thereby building a stronger regional presence in IC design and development. Additionally, the establishment of sales offices would enable us to provide sales and technical support to potential new customers.

In view of this expansion, we intend to hire personnel across these markets, including sales and technical support teams. These teams will provide pre-sale technical assistance, prepare technical proposals, and generate sales leads to drive our business growth.

As at the LPD, the status of expansion of our operational facilities in foreign markets are as follows:

- we have appointed a sales representative in the USA; and

- we have yet to identify the location for the new offices in the USA and Japan.

## (ii) Expansion of computing infrastructure, facilities and software

As part of our facility expansion plan, we will expand our computing infrastructure, facilities and software to support our operations to cater for business and product expansion plans. This expansion includes:

expansion of computing infrastructure and labs, including servers, cloud services, data storage and network equipment to handle intensive simulation, synthesis and verification tasks. These upgrades will support our complex design works, as well as enabling cloud integration for scalable simulation, verification and data storage, with backup solutions to ensure redundancy.

This also includes the purchase and/or lease of laboratory equipment such as oscilloscopes for signal integrity and timing analysis, logic analysers to analyse digital signals from prototypes, and pattern generators to generate stimulus patterns for testing silicon IP functions.

- subscription, licensing and/or purchase of EDA and development tools including validation and test tools from multiple providers to support the design and development works.

## (iii) Estimated cost for our facility and resource expansion

The estimated cost for our facility and resource expansion is approximately RM[•] million which will be funded through the gross proceeds from our Public Issue, the details of which are set out below:

|                                                                                | Estimated total cost (RM mil) | Timeline for completion |

|--------------------------------------------------------------------------------|-------------------------------|-------------------------|

| Expand operational facilities and resources                                    | [•]                           | 2026 - 2029             |

| Recruitment and IT infrastructure costs <sup>(1)</sup>                         | [•]                           | 2026 - 2029             |

| Expansion of R&D and/or sales offices <sup>(2)</sup>                           | [•]                           | 2026 - 2029             |

| Expansion of computing infrastructures, facilities and software <sup>(1)</sup> | [•]                           | 2026 - 2029             |

| Expansion of computing infrastructure and labs                                 | [•]                           | 2026 - 2029             |

| Subscription, licensing and/or purchase of EDA and development tools           | [•]                           | 2026 - 2029             |

| Total                                                                          | [•]                           |                         |

#### Notes:

- (1) Allocated for our existing operations in Malaysia and Vietnam, as well as new foreign markets including the USA and Japan in future.

- (2) Include the rental costs of the R&D and/or sales offices within 36 months from the date of our Listing.

## 7.5.5 Our product roadmap at a glance

Since our business commenced in 2020, we have progressed and expanded our product and service offerings to meet the evolving changes in the IC design industry as well as to support our business operations, growth and strategies.

For the Financial Years Under Review, we designed and commercialised several silicon IPs, including memory interface IP, Network-on-Chip IP and D2D interface IP, as well as designed and developed custom silicon IP. In addition, we also designed and commercialised the jointly developed custom ASIC.

From 2026 to 2029, we plan to expand our product portfolio to include automotive IP, custom compute and AI hardware accelerator, high-performance CPU and AI platform, as well as 2.5D/3D and other silicon products, to drive our business growth and increase our revenue base.

See Section 7.7 of this Prospectus for our current products and services, and Section 7.5 of this Prospectus for our future products and services.

## 7.6 MODE OF OPERATIONS

## (i) Silicon IP segment

For the Financial Years Under Review and up to the LPD, our arrangements with customers for the design of standard and custom silicon IPs are primarily based on lump-sum contracts secured. Contracts are secured based on submission of proposals directly to potential customers. Once all technical specifications and commercial terms have been agreed, our customers will then award the contracts.

The payment is in the form of agreed fees based on milestones stipulated in the contracts, which commonly include an initial milestone payment upon signing of the contract. For the Financial Years Under Review and up to the LPD, all revenue from our standard and custom silicon IPs is based on outright sales for the right-of-use of our IP designs.

Our customers can only use our standard and custom silicon IPs for specific projects as agreed. The use of our standard and custom silicon IPs for different projects will be subject to additional payment and conditions. Our customers commonly have the right-to-use per project and are not allowed to resell and do further development on our standard and custom silicon IPs, while we continue to own the IP rights to the design.

## (ii) Custom ASIC and other silicon products segment

As at the LPD, we have 4 contracts for the design and development of custom ASICs and other silicon products namely RISC-V SoC. Depending on the types of contracts secured, revenue is derived from design and development work completed based on the contracts, as well as product sales based on confirmed purchase orders under cost-plus arrangements.

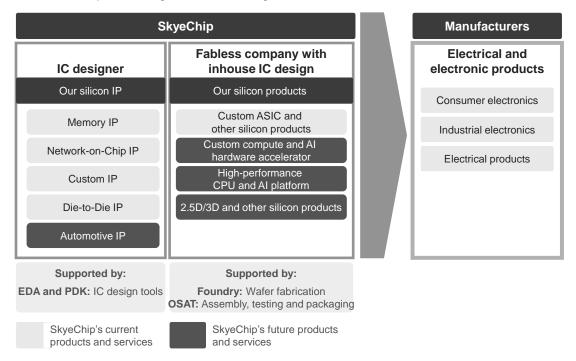

#### 7.7 PRODUCTS AND SERVICES

#### 7.7.1 Overview

We are an IC design company specialising in silicon IPs, including standard silicon IPs and custom silicon IPs as well as silicon products including custom ASIC.

An IC is a miniature electronic device made up interconnected transistors. resistors. capacitors and other components etched onto a small piece of semiconductor material. usually silicon.

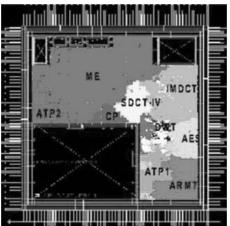

Part of an IC diagram we would normally design

Connections in the context of ICs are conductive paths that allow electrical signals to move between different components and devices on the chip. They enable communications and interactions between various parts of the circuit.

Silicon IP refers to complex pre-designed and reusable functional blocks or modules of circuitry. These blocks can operate as standalone chips or be integrated into larger ICs to perform specific functions, such as processing or communication. Our IPs are pre-designed and preverified modules that simplify the design process for chip designers by eliminating the need for extensive design, verification and testing of these functional cores.

The term 'IP' in relation to our IC indicates that we are the original designer and owner of the intellectual property associated with our IC. This allows us to resell or reconfigure our silicon IP for any customer of our choice.

A custom ASIC is a semiconductor chip designed for a specific application rather than for generalpurpose use.

Once we have completed our design of silicon IP, they are compiled into several file formats which are digital formats and may be transmitted over a normal network such as the internet, or stored in a normal data storage device.

Our silicon IPs are commonly integrated with other ICs to form larger systems, such as SoC, CPU and FPGA (a type of functionally reconfigurable IC). These integrated systems are then

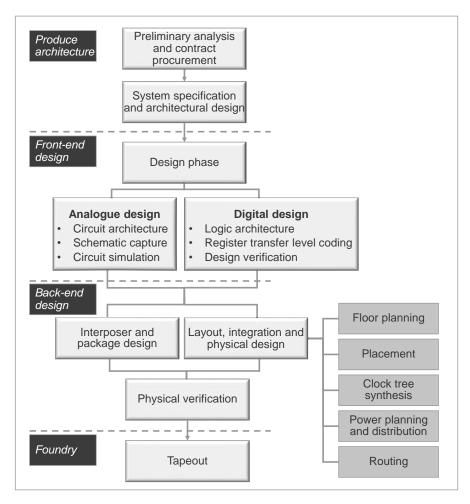

#### Our position within the value chain of producing a chip

sent to a foundry for IC die fabrication. Finally, the semiconductor company packages the die into a finished chip, which is then assembled onto a motherboard for inclusion into a device.

For silicon IP designs, we undertake comprehensive end-to-end design and development. This process includes system specification; architectural, functional, logic, circuitry and physical design; as well as verification and testing. Our verification process involves simulations, timing analysis and design rule compliance checks. We also develop testbenches and simulation environments to validate the functionality and performance of our IPs.

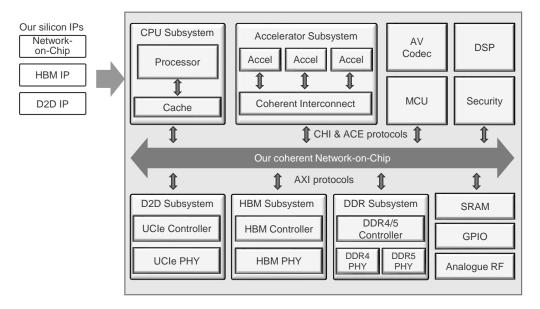

The following diagram illustrates our silicon IP within a larger processing system:

## Note:

$HBM = high-bandwidth\ memory;\ D2D = die-to-die;\ Accel = accelerator;\ MCU = microcontroller\ unit;\ DSP = digital\ signal\ processing;\ SRAM = static\ random-access\ memory;\ GPIO = general-purpose\ input/output;\ analogue\ RF = analogue\ radio\ frequency;\ PHY = physical\ layer$

Our technical personnel team is equipped with the know-how of designing silicon IPs and products, with the aid of EDA tools, in advanced process technologies including via PDKs from foundries. EDA tools are software tools that enable us to carry out the design, verification and testing processes, while the PDKs enable us to access technologies from foundries to ensure our IC designs are compatible with the foundry fabrication technologies and processes such as fabricating ICs using process nodes down to 4nm.

We collaborate with EDA tool providers to develop our designs using their tools, such as simulators, modelling systems and logic and physical synthesis tools. Additionally, we participate in final design reviews conducted with customers and foundries to ensure that our IP designs are integrated in line with specified requirements. This process is concluded with the 'tapeout' phase, indicating that our design has been approved and is ready for fabrication into silicon products.

Our technical capabilities are also enhanced by our continuous R&D as demonstrated by our track record of being providers of various memory interface IPs for DDR, LPDDR and HBM. Additionally, our R&D has enabled us to patent our works. As at the LPD, we have 29 patents registered in Malaysia, China and the USA, and 79 patents pending application/registration in Malaysia, China and the USA.

As at the LPD, we have a total of 318 technical personnel including engineers led by our Chief Technology Officer, Teh Chee Hak. Our IC design capabilities include the following:

- Advanced process node expertise: We are proficient in designing IP and IC using advanced process nodes down to 4nm, facilitated by access to the relevant PDKs.

- High-speed memory interfaces: We have successfully designed and commercialised high-performance memory interfaces such as DDR4/5 with per pin data rate up to 3200 MT/s, LPDDR4x with data rate per pin up to 4267 MT/s, and HBM3 with data rate per pin up to 6.4 Gb/s. Our latest HBM3E is designed to achieve data rate per pin up to 8.0 Gb/s and above.

- Custom silicon IP development: We develop custom silicon IPs, tailored to specific application requirements and performance targets, including ASICs.

- **Integration with EDA tools**: We utilise EDA tools to streamline our design process for silicon IP and custom ASIC development.

- **On-chip high-speed interconnects**: We design on-chip high-speed interconnects such as Network-on-Chip architecture for efficient data transfer and integration in complex systems.

- **Precision in timing and signal integrity**: Our design enables high-speed data transfer by addressing timing and signal integrity requirements through precise modelling and simulation, especially in high-speed memory interfaces and Network-on-Chip interconnects.

- **Integration expertise**: Our design enables seamless integration of memory interfaces and on-chip interconnects within multi-processor systems, using our in-house developed integration and configuration software, namely RAPTuner for integration with our Network-on-Chip.

#### 7.7.2 Standard and custom silicon IPs

Our design and development of silicon IP can be broadly categorised into standard and custom silicon IPs as follows:

## (i) Standard silicon IP

We design standard silicon IP that adheres to industry specifications, such as JEDEC and UCle standards. Our standard silicon IPs include memory interface IP, Network-on-Chip IP, and D2D interface IP. See Sections 7.7.3 to 7.7.7 of this Prospectus for further details of memory interface IP and Network-on-Chip IP.

## (ii) Custom silicon IP

Custom silicon IPs are typically designed to meet specific performance, power and area requirements, or to offer enhanced or extended features customised to particular customer specifications to ensure optimal integration and functionality for customers' products.

We design and develop custom silicon IPs with the following features:

- multi-interface protocols that can support different standards or communication protocols such as DDR and LPDDR memory interfaces, MIPI interfaces, LVDS interfaces and GPIO interfaces. These multi-interface protocols often incorporate bridging mechanisms which enable data to be translated or converted between different protocol types seamlessly, enabling communications across systems (such as CPU, memory and sensors).

- low-power low-latency memory interface features designed to minimise power consumption and optimise memory protocol handling for data flow between compute cores and memory, which are targeted for wearables.

## 7.7.3 Memory interface silicon IP

We design the IP for the memory interface core. A memory interface core is a specialised module or functional block to facilitate communications between a memory device and a digital logic device.

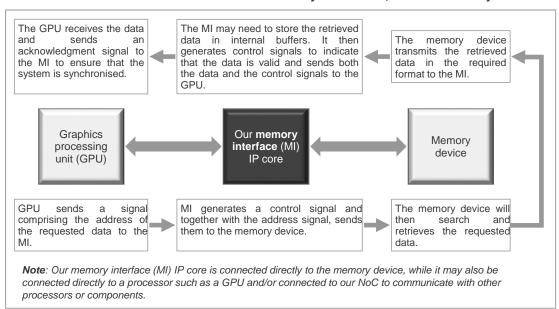

#### Illustration of the interaction between our memory interface IP, GPU and memory device

Our memory interface IP is crucial in IC design to ensure efficient and reliable communication between the memory and the processing unit or logic device, which affects overall system performance and functionality.

Some of the key functions of our memory interface IP include the following:

- **Protocol handling**: Our memory interface IP implements the specific communication protocols and manages the control and address signals, data transfer and acknowledgements required by various memory types, such as DDR, LPDDR and HBM interfaces.

- Data buffers: Our memory interface IP uses data buffers to temporarily store data for synchronisation between the processor and memory, as well as to reorder data for more efficient processing.

- **Timing management**: Our memory interface IP manages clock signals and timing parameters for read (data retrieval) and write (data storage) operations to synchronise these actions and avoid conflicts or out-of-sequence read/write operations.

- Error correction: Our memory interface IP also includes error detection and correction capabilities (such as error correction code) to ensure reliability and data quality during data transfers.

- Power management: Our memory interface IP often incorporates power management features to optimise energy consumption, particularly important in mobile and embedded applications.

- Configuration and initialisation: Our memory interface IP typically includes functions for configuring and initialising memory devices, ensuring that they are correctly set up correctly and trained before use.

Our memory interfaces are used for the following applications:

- **Memory and CPU interface**: This is the most common application, where memory interfaces connect the system's memory (random-access memory) to the CPU. This ensures data and instructions are efficiently transferred between these components.

- **Memory and GPU interface**: In systems with a GPU, memory interfaces connect the GPU to its dedicated memory such as HBM. This is essential for high-bandwidth data transfer required for graphics processing.

- **Memory and other accelerators**: Memory interfaces are used to connect memory to other accelerators, such as DSPs, network interface controllers or custom hardware accelerators. This helps in offloading specific tasks from the CPU and improving overall system performance.

- **Memory and network interfaces**: For high-performance networking applications, memory interfaces may connect to network traffic management ASICs or other network components, facilitating high-speed data transfer and buffering.

- **Inter-processor communication**: In multi-processor or multi-core systems, memory interfaces can be used to facilitate communication between different processors or cores. This includes sharing data between processors in a multi-core CPU or between different chips in a SoC.

- **Memory hierarchies**: In complex systems, memory interfaces help manage various levels of memory hierarchy, such as cache memory, main memory and off-chip memory. Efficient interfaces are crucial for maintaining optimal performance across these different memory hierarchy levels.

Our memory interface IPs adhere to JEDEC standards to ensure interoperability and reliability, focus on increased data rates for faster data transfers, power efficiency optimisation and maintaining signal integrity.

Our memory interface IPs are pre-designed and pre-verified, which enables us to either resell it as-is or quickly reconfigure it for use in different applications and for different customers instead of designing the memory interface core from scratch.

Our memory interface IP also operates through a memory interface IP firmware, in which the development is carried out in-house. This firmware is crucial for ensuring the functionality, efficiency and compatibility of our memory interface IP with various memory technologies and suppliers. Some of the functionalities of the firmware that we develop include the following:

- Perform initialisation, configuration and training sequences to initialise and configure the memory device.

- Performance optimisation including timing analysis to ensure that the memory interface meets the required timing constraints, and to optimise the design to achieve the desired throughput and latency metrics.

- System compatibility to ensure that the memory interface integrates smoothly with other IPs in the system such as CPU and GPU.

- Power management to optimise power consumption of the memory interface, and to handle low-power modes and power-saving features.

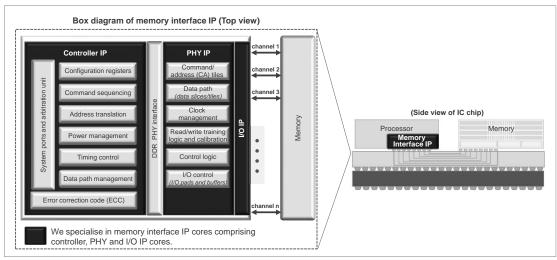

Our comprehensive memory interface IP integrates multiple functionalities, including a memory controller IP and PHY IP as follows:

• **Memory controller IP**: The memory controller IP is designed to manage communication between the memory subsystem and processor or other system components. It handles the logical operations required to read from and write to the memory according to the specific memory standard in use. This involves translating the processor's requests into appropriate commands for tasks such as initialisation, refresh, power-down, error correction and data flow management.

The design of the memory controller IP incorporates the following considerations and parameters:

- Command sequencing: Converts memory commands from the processor into sequences of commands suitable for the memory device. This includes managing the proper sequencing and timing of commands to ensure correct operation.

- Address translation: Maps virtual addresses used by the processor to physical addresses in the memory device. This ensures that data is correctly located and accessed.

- Data path management: Manages the data path for read and write to ensure data integrity and proper timing. This involves designing data queues that support the transfer of data signals between the controller and the memory devices. The number of data queue lines varies depending on the memory type and configuration.

- Timing control: Ensures that memory operations adhere to timing constraints specified by standards such as DDR5 and HBM3. This includes managing signal timing to meet performance requirements.

- Error correction: Implements error detection and correction algorithms to maintain data integrity and reliability. This ensures that data errors are detected and corrected as needed.

- Power management: Incorporates features to reduce energy consumption, especially during idle periods, to enhance overall power efficiency.

PHY IP: The PHY IP is designed to manage the physical data transmission, handling

the electrical and timing characteristics required for the connection between the

processor and memory devices. It converts digital signals from the memory controller

into the appropriate physical signals for the memory device. This ensures that electrical

signals are accurately converted and timed to maintain reliable and high-speed data

transfer.

The design of the PHY IP incorporates the following considerations and parameters:

- Signal integrity: Ensures minimal distortion and noise during signal transmission, maintaining high-quality data transfer.

- Timing calibration and management: Provides precise timing control to meet the stringent requirements of high-speed memory interfaces, ensuring accurate data transmission.

- Interface standards: Adheres to physical interface standards based on the memory technology used, such as DDR, LPDDR or HBM. This ensures compatibility with various memory types and configurations.

- Calibration: Maintains optimal signal integrity and performance through calibration processes. This includes data serialisation and deserialisation, converting parallel data from the memory controller into a serial form for transmission, and then converting it back to parallel form upon reception.